Famiglie logiche

Le porte logiche (Gates) realizzano delle funzioni logiche elementari ma combinandole opportunamente si realizzano sistemi molto piu' complessi.

I circuiti logici esistenti in commercio vengono suddivisi in famiglie a seconda del tipo di tecnologia con cui vengono realizzati.

Le famiglie più diffuse sono essenzialmente due:

- CMOS basate sulla tecnologia MOS

- TTL basate sulla tecnologia a BJT

La famglia delle CMOS è molto più flessibile sia per quanto riguarda la tensione di alimentazione , Vcc che va da 3V a 15V, sia per i range di tensione interpretati in ingresso come 1 o 0

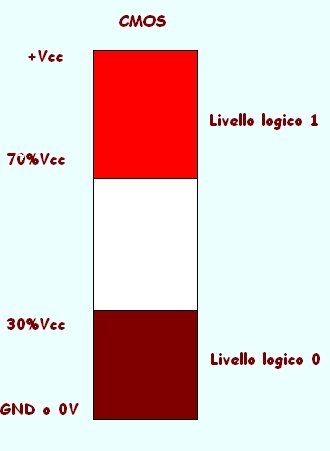

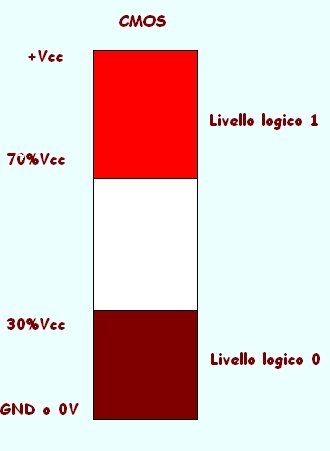

Come livello logico 0 viene riconosciuto un segnale la cui tensione oscilla tra 0 V e il 30% della tensione di alimentazione, mentre viene interpretato come 1 logico un segnale compreso tra il 70% della tensione di alimentazione e il valore della tensione di alimentazione stessa.

Il segnale di uscita può avere solamente due valori :

-Vcc , tensione di alimentazione della porta logica, detto livello logico 1

-GND o 0 Volt detto livello logico 0

Alimentandole con 12V il segnale di uscita può portarsi ad un livello di tensione di 12V (livello logico 1) o di 0 V (ivello logico 0).

In ingresso sarà interpretatocome 0 logico un segnale compreso tra 0 V e 3.6 V, mentre sarà riconosciuto come 1 logico un segnale compreso tra 8.4 e 12V

Esitono delle porte logiche con uscita a 3 stati, infatti ai soliti stati logici 1 o H ed 0 o L , l'uscita puo' assumere un terzo stato detto ad "alta impedenza"

In questo caso si ha una sconnesione virtuale dell'uscita dal resto del circuito.

I principali parametri caratteristici delle porte logiche sono riportati nei datasheet rilasciati dal costruttore come la Vcc di lavoro, temperature di funzionamento, la potenza media dissipata dalla porta, le frequenze di funzionamento, la caricabilità in uscita (fan out), il numero di dispositivi collegabili in ingresso (fan in), tempo di propagazione di un segnale dall'ingresso all'uscita (propagation. delay).

Porte logiche elementari

|

|

|

Porte logiche derivate

|

|

|

|

EX-NOR

|

||

|

ingresso A

|

Ingresso B

|

uscita Y

|

|

0

|

0

|

1

|

|

0

|

1

|

0

|

|

1

|

0

|

0

|

|

1

|

1

|

1

|